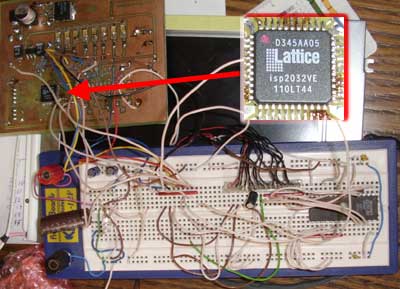

I decided to connect LCD monitor to my CPLD project. LCD monitor is without frame buffer RAM, without controller- just simple LCD matrix. All data is dynamically fed to LCD. For my first experiments I was using Lattice isp2032VE. The programming software is very simple, configuration is stored in nonvolatile flash memory. But it is small chip. The number of pins is good, the package is very good, but I am lacking of internal logic power.

Here is my “workbench”. The ROM is imitating video RAM- the contents of the ROM is displayed on the screen. I must receive chaotic, but static image. All signals: vertical and horizontal sync signals, pixel clock and address are generated from master clock by CPLD. But I reached the margin of this chip- if I add single pin I receive message: “34200 ERROR: Number of GLBs, 9, exceeds maximum number of available GLBs, 8, in part ‘ispLSI2032VE-110LT44’ “.

But I need at least 11 pins more! I searched my archive again… I have ispLSI2128-100LT… but it is unsupported by demo software. Or something wrong with my PCB.

I was forced to change chip family. In some old DSL modem I found ALTERA’s Flex chip. Using air gun I blowed away almost everything and left only FPGA, power regulator, some RTC chips and LEDs with drivers. Now I have something like experimental board- the JTAG port is routed in this board.

ALTERA’s software differs from Lattice. I need to learn few tricks again. The programmer detected my chip and I traced all usable pins: LEDs, test points, switches…